## Numbering

20140603 DRAFT 20140604 First version

All numbering is assuming that one look towards the LPTPC end plate from the outside. MCM = Multi Chip Module LV board = Low Voltage board

## MCM

On the MCM board the "top" side refers to the side facing away from the pad plane and the "bottom" side refers to the side facing towards the pad plane.

All numbering of connectors and chips on the MCM is from right to left, and increasing from a thought collision point and radially outwards.

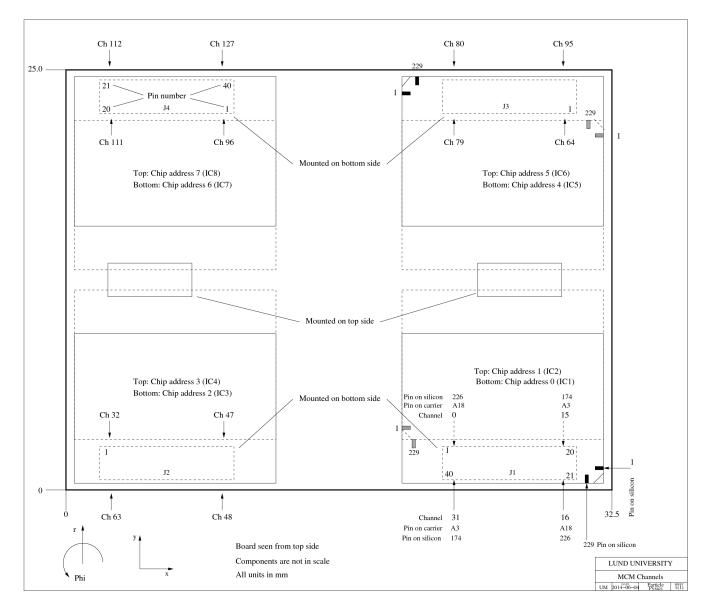

In the figures the dashed lines are referring to components on the bottom side, and solid lines are referring to components on the top side.

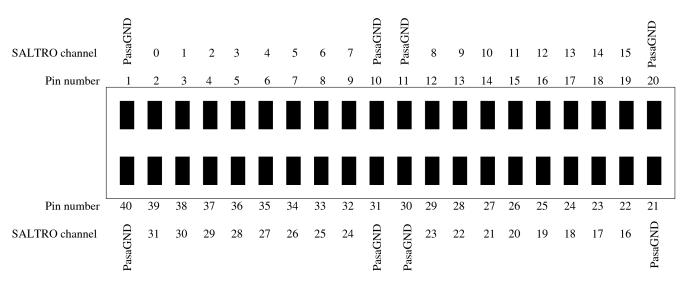

The connectors between the pad plane and the MCM board is rotational symmetric, and has no predefined pin numbering by the manufacturer. Our pin numbering is defined such that they follow the order of the SALTRO channels. This is shown in figure 1. The connector shown in figure 1 corresponds to the orientation and location of connector J1 in figure 2, i.e. as seen from the outside and towards the pad plane.

Each connector handles input signals for two SALTRO chips. Channel 0-15 refers to the chip on the bottom side and channel 16-31 refers to the chip on the top side. Eight pins are used to connect the SALTRO PasaGND to the ground on the pad plane.

There are four such connectors, on the MCM called J1 to J4. Each SALTRO has a unique Chip Address (CA). The chip addresses (CA) is between 0 and 7. On the MCM schematic these chips are labeled IC1 to IC8.

| Location    | Side   | Connect<br>or | Pins on<br>connector | Chip<br>Address | MCM<br>channel | MCM<br>label |

|-------------|--------|---------------|----------------------|-----------------|----------------|--------------|

| Lower right | Bottom | J1            | 1-20                 | 0               | 0-15           | IC1          |

| Lower right | Тор    | J1            | 21-40                | 1               | 16-31          | IC2          |

| Lower left  | Bottom | J2            | 1-20                 | 2               | 32-47          | IC3          |

| Lower left  | Тор    | J2            | 21-40                | 3               | 48-63          | IC4          |

| Upper right | Bottom | J3            | 1-20                 | 4               | 64-79          | IC5          |

| Upper right | Тор    | J3            | 21-40                | 5               | 80-95          | IC6          |

| Upper left  | Bottom | J4            | 1-20                 | 6               | 96-111         | IC7          |

| Upper left  | Тор    | J4            | 21-40                | 7               | 112-127        | IC8          |

Even CA (odd chip labels) are on the bottom side, odd CA (even chip labels) are on the top side. The physical location on the MCM of connectors (J1-J4) and CA (0-7) are given in table 1.

Table 1

where lower is closest to a thought collision point, and upper is in the outward radial direction.

An MCM is shown in figure 2, showing the numbering, orientation and location of chips and connectors. Included is also the pin numbers 1 and 229 on the SALTRO silicon and A3 and A18 on the carrier board. The orientation of the SALTRO is indicated by the pins 1 and 229 on the silicon and the symbol indicating the corner with these pin numbers. Note that only lower right part is fully drawn, other parts are indicated. *Note that the upper connectors (J3 and J4) are rotated 180 degrees with respect to J1 and J2*.

Figure 2

The channel number on an MCM is 0-127 = i \* 16 + c, where i = 0 to 7 (Chip Address), c=0 to 15 (channel).

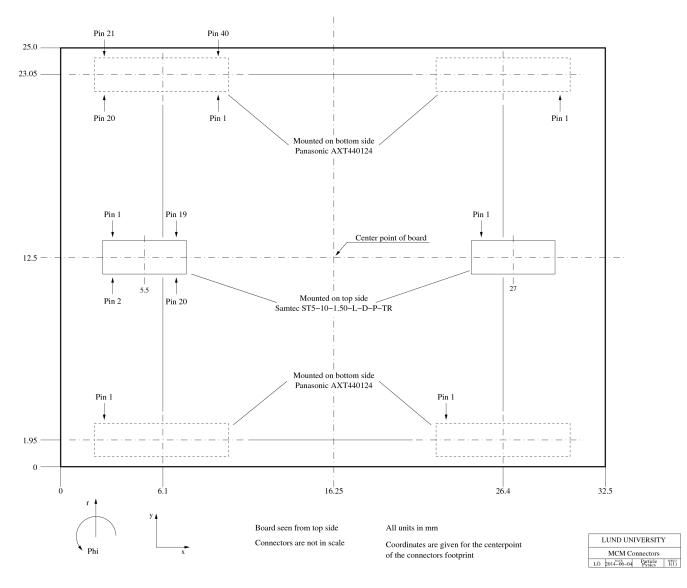

Figure 3

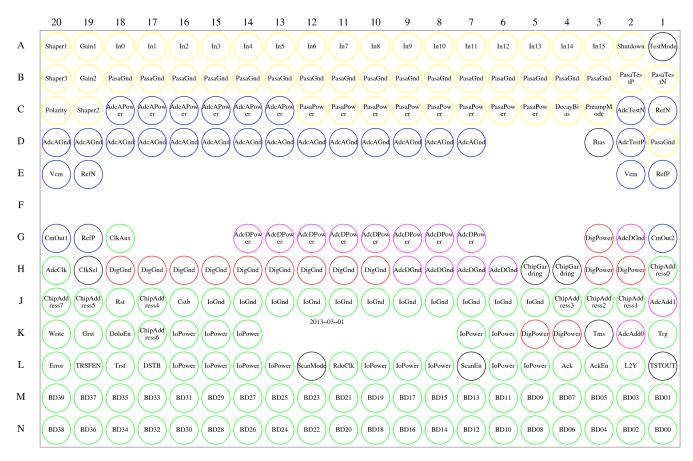

The pin numbering on the carrier board, as seen from the side with the SALTRO chip, is shown in figure 4. The input signals In0 to In15 are on pins A18 to A3.

Figure 4

## MCM and LV board numbering within a pad module

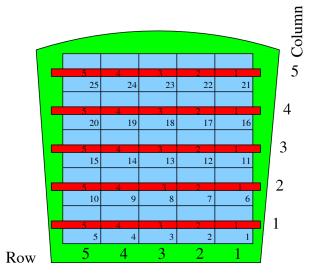

The MCMs (in blue) are numbered 1-25, see figure 5, as (column - 1)\*5 + row. With MCM 1 in lower right corner and 25 in upper left. The LV boards (in red) are numbered as the column number (1-5) and the MCM within a LV board as the row number (1-5). The LV board and MCMs are configured and monitored through a Detector Control System, where the interface to each LV board is via a CPU on a 5to1 board. Each 5to1 board has 5 CPUs, each CPU can handle one LV board with 5 MCMs. The CPUs on the 5to1 board is numbered as the column number (1-5), i.e. the same numbering as for the LV boards.

Figure 5

The channel numbering within a pad plane is between 0 - 3199: (MCM number -1) \* 128 + (Chip Address \* 16) + channel in chip